FPGA是(shì)英文Field-Programmable Gate Array的(de)縮寫,即現場可編程門陣列,它是(shì)在(zài)PAL、GAL、CPLD等可編程器件的(de)基礎上(shàng)進一(yī / yì /yí)步發展的(de)産物。它是(shì)作爲(wéi / wèi)專用集成電路(ASIC)領域中的(de)一(yī / yì /yí)種半定制電路而(ér)出(chū)現的(de),既解決了(le/liǎo)定制電路的(de)不(bù)足,又克服了(le/liǎo)原有可編程器件門電路數有限的(de)缺點。

【FPGA工作原理】

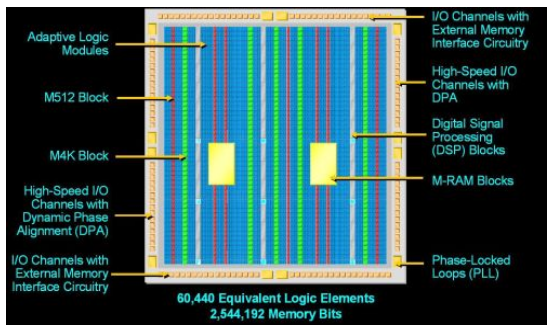

FPGA采用了(le/liǎo)邏輯單元陣列LCA(Logic Cell Array)這(zhè)樣一(yī / yì /yí)個(gè)新概念,内部包括可配置邏輯模塊CLB(Configurable Logic Block)、輸出(chū)輸入模塊IOB(Input Output Block)和(hé / huò)内部連線(Interconnect)三個(gè)部分。FPGA的(de)基本特點主要(yào / yāo)有:

1)采用FPGA設計ASIC電路,用戶不(bù)需要(yào / yāo)投片生産,就(jiù)能得到(dào)合用的(de)芯片。

2)FPGA可做其它全定制或半定制ASIC電路的(de)中試樣片。

3)FPGA内部有豐富的(de)觸發器和(hé / huò)I/O引腳。

4)FPGA是(shì)ASIC電路中設計周期最短、開發費用最低、風險最小的(de)器件之(zhī)一(yī / yì /yí)。

5) FPGA采用高速CHMOS工藝,功耗低,可以(yǐ)與CMOS、TTL電平兼容。

可以(yǐ)說(shuō),FPGA芯片是(shì)小批量系統提高系統集成度、可靠性的(de)最佳選擇之(zhī)一(yī / yì /yí)。

FPGA是(shì)由存放在(zài)片内RAM中的(de)程序來(lái)設置其工作狀态的(de),因此,工作時(shí)需要(yào / yāo)對片内的(de)RAM進行編程。用戶可以(yǐ)根據不(bù)同的(de)配置模式,采用不(bù)同的(de)編程方式。

加電時(shí),FPGA芯片将EPROM中數據讀入片内編程RAM中,配置完成後,FPGA進入工作狀态。掉電後,FPGA恢複成白片,内部邏輯關系消失,因此,FPGA能夠反複使用。FPGA的(de)編程無須專用的(de)FPGA編程器,隻須用通用的(de)EPROM、PROM編程器即可。當需要(yào / yāo)修改FPGA功能時(shí),隻需換一(yī / yì /yí)片EPROM即可。這(zhè)樣,同一(yī / yì /yí)片FPGA,不(bù)同的(de)編程數據,可以(yǐ)産生不(bù)同的(de)電路功能。因此,FPGA的(de)使用非常靈活。

【FPGA配置模式】

FPGA有多種配置模式:并行主模式爲(wéi / wèi)一(yī / yì /yí)片FPGA加一(yī / yì /yí)片EPROM的(de)方式;主從模式可以(yǐ)支持一(yī / yì /yí)片PROM編程多片FPGA;串行模式可以(yǐ)采用串行PROM編程FPGA;外設模式可以(yǐ)将FPGA作爲(wéi / wèi)微處理器的(de)外設,由微處理器對其編程。

如何實現快速的(de)時(shí)序收斂、降低功耗和(hé / huò)成本、優化時(shí)鍾管理并降低FPGA與PCB并行設計的(de)複雜性等問題,一(yī / yì /yí)直是(shì)采用FPGA的(de)系統設計工程師需要(yào / yāo)考慮的(de)關鍵問題。如今,随着FPGA向更高密度、更大(dà)容量、更低功耗和(hé / huò)集成更多IP的(de)方向發展,系統設計工程師在(zài)從這(zhè)些優異性能獲益的(de)同時(shí),不(bù)得不(bù)面對由于(yú)FPGA前所未有的(de)性能和(hé / huò)能力水平而(ér)帶來(lái)的(de)新的(de)設計挑戰。

例如,領先FPGA廠商Xilinx最近推出(chū)的(de)Virtex-5系列采用65nm工藝,可提供高達33萬個(gè)邏輯單元、1,200個(gè)I/O和(hé / huò)大(dà)量硬IP塊。超大(dà)容量和(hé / huò)密度使複雜的(de)布線變得更加不(bù)可預測,由此帶來(lái)更嚴重的(de)時(shí)序收斂問題。此外,針對不(bù)同應用而(ér)集成的(de)更多數量的(de)邏輯功能、DSP、嵌入式處理和(hé / huò)接口模塊,也(yě)讓時(shí)鍾管理和(hé / huò)電壓分配問題變得更加困難。

幸運地(dì / de)是(shì),FPGA廠商、EDA工具供應商正在(zài)通力合作解決65nm FPGA獨特的(de)設計挑戰。不(bù)久以(yǐ)前,Synplicity與Xilinx宣布成立超大(dà)容量時(shí)序收斂聯合工作小組,旨在(zài)最大(dà)程度幫助地(dì / de)系統設計工程師以(yǐ)更快、更高效的(de)方式應用65nm FPGA器件。設計軟件供應商Magma推出(chū)的(de)綜合工具Blast FPGA能幫助建立優化的(de)布局,加快時(shí)序的(de)收斂。

最近FPGA的(de)配置方式已經多元化!

【FPGA主要(yào / yāo)生産廠商介紹】

1、Altera

2、Xilinx

3、Actel

4、Lattice

其中Altera和(hé / huò)Xilinx主要(yào / yāo)生産一(yī / yì /yí)般用途FPGA,其主要(yào / yāo)産品采用RAM工藝。Actel主要(yào / yāo)提供非易失性FPGA,産品主要(yào / yāo)基于(yú)反熔絲工藝和(hé / huò)FLASH工藝。

【FPGA設計的(de)注意事項】

不(bù)管你是(shì)一(yī / yì /yí)名邏輯設計師、硬件工程師或系統工程師,甚或擁有所有這(zhè)些頭銜,隻要(yào / yāo)你在(zài)任何一(yī / yì /yí)種高速和(hé / huò)多協議的(de)複雜系統中使用了(le/liǎo)FPGA,你就(jiù)很可能需要(yào / yāo)努力解決好器件配置、電源管理、IP集成、信号完整性和(hé / huò)其他(tā)的(de)一(yī / yì /yí)些關鍵設計問題。不(bù)過,你不(bù)必獨自面對這(zhè)些挑戰,因爲(wéi / wèi)在(zài)當前業内領先的(de)FPGA公司裏工作的(de)應用工程師每天都會面對這(zhè)些問題,而(ér)且他(tā)們已經提出(chū)了(le/liǎo)一(yī / yì /yí)些将令你的(de)設計工作變得更輕松的(de)設計指導原則和(hé / huò)解決方案。

I/O信号分配

可提供最多的(de)多功能引腳、I/O标準、端接方案和(hé / huò)差分對的(de)FPGA在(zài)信号分配方面也(yě)具有最複雜的(de)設計指導原則。盡管Altera的(de)FPGA器件沒有設計指導原則(因爲(wéi / wèi)它實現起來(lái)比較容易),但賽靈思的(de)FPGA設計指導原則卻很複雜。但不(bù)管是(shì)哪一(yī / yì /yí)種情況,在(zài)爲(wéi / wèi)I/O引腳分配信号時(shí),都有一(yī / yì /yí)些需要(yào / yāo)牢記的(de)共同步驟:

1. 使用一(yī / yì /yí)個(gè)電子(zǐ)數據表列出(chū)所有計劃的(de)信号分配,以(yǐ)及它們的(de)重要(yào / yāo)屬性,例如I/O标準、電壓、需要(yào / yāo)的(de)端接方法和(hé / huò)相關的(de)時(shí)鍾。

2. 檢查制造商的(de)塊/區域兼容性準則。

3. 考慮使用第二個(gè)電子(zǐ)數據表制訂FPGA的(de)布局,以(yǐ)确定哪些管腳是(shì)通用的(de)、哪些是(shì)專用的(de)、哪些支持差分信号對和(hé / huò)全局及局部時(shí)鍾、哪些需要(yào / yāo)參考電壓。

4. 利用以(yǐ)上(shàng)兩個(gè)電子(zǐ)數據表的(de)信息和(hé / huò)區域兼容性準則,先分配受限制程度最大(dà)的(de)信号到(dào)引腳上(shàng),最後分配受限制最小的(de)。例如,你可能需要(yào / yāo)先分配串行總線和(hé / huò)時(shí)鍾信号,因爲(wéi / wèi)它們通常隻分配到(dào)一(yī / yì /yí)些特定引腳。

5. 按照受限制程度重新分配信号總線。在(zài)這(zhè)個(gè)階段,可能需要(yào / yāo)仔細權衡同時(shí)開關輸出(chū)(SSO)和(hé / huò)不(bù)兼容I/O标準等設計問題,尤其是(shì)當你具有很多個(gè)高速輸出(chū)或使用了(le/liǎo)好幾個(gè)不(bù)同的(de)I/O标準時(shí)。如果你的(de)設計需要(yào / yāo)局部/區域時(shí)鍾,你将可能需要(yào / yāo)使用高速總線附近的(de)管腳,最好提前記住這(zhè)個(gè)要(yào / yāo)求,以(yǐ)免最後無法爲(wéi / wèi)其安排最合适的(de)引腳。如果某個(gè)特定塊所選擇的(de)I/O标準需要(yào / yāo)參考電壓信号,記住先不(bù)要(yào / yāo)分配這(zhè)些引腳。差分信号的(de)分配始終要(yào / yāo)先于(yú)單端信号。如果某個(gè)FPGA提供了(le/liǎo)片内端接,那麽它也(yě)可能适用于(yú)其他(tā)兼容性規則。

6. 在(zài)合适的(de)地(dì / de)方分配剩餘的(de)信号。

在(zài)這(zhè)個(gè)階段,考慮寫一(yī / yì /yí)個(gè)隻包含端口分配的(de)HDL文件。然後通過使用供應商提供的(de)工具或使用一(yī / yì /yí)個(gè)文本編輯器手動創建一(yī / yì /yí)個(gè)限制文件,爲(wéi / wèi)I/O标準和(hé / huò)SSO等增加必要(yào / yāo)的(de)支持信息。準備好這(zhè)些基本文件後,你可以(yǐ)運行布局布線工具來(lái)确認是(shì)否忽視了(le/liǎo)一(yī / yì /yí)些準則或者做了(le/liǎo)一(yī / yì /yí)個(gè)錯誤的(de)分配。

這(zhè)将使你在(zài)設計的(de)初始階段就(jiù)和(hé / huò)布局工程師一(yī / yì /yí)起工作,共同規劃PCB的(de)走線、冗餘規劃、散熱問題和(hé / huò)信号完整性。FPGA工具可能可以(yǐ)在(zài)這(zhè)些方面提供幫助,并協助你解決這(zhè)些問題,因此你必須确保了(le/liǎo)解你的(de)工具包的(de)功能。

你咨詢一(yī / yì /yí)位布局專家的(de)時(shí)間越晚,你就(jiù)越有可能需要(yào / yāo)去處理一(yī / yì /yí)些複雜的(de)問題和(hé / huò)設計反複,而(ér)這(zhè)些可能可以(yǐ)通過一(yī / yì /yí)些前期分析加以(yǐ)避免。一(yī / yì /yí)旦你實現了(le/liǎo)滿意的(de)信号分配,你就(jiù)要(yào / yāo)用限制文件鎖定它們。

-------------------

基于(yú)CMOS的(de)設計主要(yào / yāo)消耗三類切率:内部的(de)(短路)、漏電的(de)(靜态的(de))以(yǐ)及開關的(de)(電容)。當門電路瞬變時(shí),VDD與地(dì / de)之(zhī)間短路連接消耗内部功率。漏電功耗是(shì)CMOS工藝普遍存在(zài)的(de)寄生效應引起的(de)。而(ér)開關功耗則是(shì)自負載電容,放電造成的(de)。開關功耗與短路功耗合在(zài)一(yī / yì /yí)起稱爲(wéi / wèi)動态功耗。下面介紹降低靜态功耗和(hé / huò)動态功耗的(de)設計技巧。

降低靜态功耗

雖然靜态電流與動态電流相比可以(yǐ)忽略不(bù)計,然而(ér)對電池供電的(de)手持設備就(jiù)顯得十分重要(yào / yāo),在(zài)設備通電而(ér)不(bù)工作時(shí)更是(shì)如此。靜态電流的(de)因素衆多,包括處于(yú)沒有完全關斷或接通的(de)狀态下的(de)I/O以(yǐ)及内部晶體管的(de)工作電流、内部連線的(de)電阻、輸入與三态電驅動器上(shàng)的(de)拉或下拉電阻。在(zài)易失性技術中,保持編程信息也(yě)需一(yī / yì /yí)定的(de)靜态功率。抗熔斷是(shì)一(yī / yì /yí)種非易失性技術,因此信息存儲不(bù)消耗靜态電流。

下面介紹幾種降低靜态功耗的(de)設計方法:

◇驅動輸入應有充分的(de)電壓電平,因而(ér)所有晶體管都是(shì)完全通導或關閉的(de)。

◇由于(yú)I/O線上(shàng)的(de)上(shàng)拉或下拉電阻要(yào / yāo)消耗一(yī / yì /yí)定的(de)電流,因此盡量避免使用這(zhè)些電阻。

◇少用驅動電阻或雙極晶體管,這(zhè)些器件需維持一(yī / yì /yí)個(gè)恒定電流,從而(ér)增加了(le/liǎo)靜态電流。

◇将時(shí)鍾引腳按參數表推薦條件連接至低電平。懸空的(de)時(shí)鍾輸入會大(dà)大(dà)增加靜态電流。

◇在(zài)将設計劃分爲(wéi / wèi)多個(gè)器件時(shí),減少器件間I/O的(de)使用。

eX器件LP方式引腳的(de)使用

Actel eX系列設計了(le/liǎo)特殊的(de)低功率“休眠”模式。在(zài)該引腳驅動至高電平800ns後,器件進入極低功率待機模式,待機電流小于(yú)100μA。在(zài)低功率模式下,所有I/O(除時(shí)鍾輸入外)都處于(yú)三态,而(ér)内核全部斷電。由于(yú)内核被斷電,觸發器中存儲的(de)信息會丢失,在(zài)進入工作模式(在(zài)引腳驅動至低平200ms後)時(shí),用戶需再次對器件初始化。同樣,用戶也(yě)應關閉所有通過CLKA、CLKB以(yǐ)及HCLK輸入的(de)時(shí)鍾。然而(ér)這(zhè)些時(shí)鍾并不(bù)處于(yú)三态,時(shí)鍾就(jiù)可進入器件,從而(ér)增加功耗,因此在(zài)低功率模式下,時(shí)鍾輸入必須處于(yú)邏輯0或邏輯1。

有時(shí)用戶很難阻止時(shí)鍾進入器件。在(zài)此場合,用戶可使用與CLKA或CLKA相鄰的(de)正常輸入引腳并在(zài)設計中加進CLKINT。這(zhè)樣,時(shí)鍾将通過靠近時(shí)鍾引腳的(de)正常輸入進入器件,再通過CLKINT向器件提供時(shí)鍾資源。

采用這(zhè)種輸入電路後,由于(yú)常規I/O是(shì)三态的(de),因此用戶不(bù)必擔心時(shí)鍾進入器件。當然,增加一(yī / yì /yí)級門電路會産生0.6ns的(de)較大(dà)時(shí)鍾延時(shí),幸好這(zhè)在(zài)多數低功率設計中是(shì)可以(yǐ)接受的(de)。注意應将與CLKINT緩沖器相關的(de)CLKA或CLKB引腳接地(dì / de)。

此外還要(yào / yāo)注意,CLKINT隻可用作連線時(shí)鍾,HCLK并不(bù)具備将内部走線網連接到(dào)HCLK的(de)能力,因而(ér)HCLK資源不(bù)能被常規輸入驅動。換句話說(shuō),如果使用LP引腳就(jiù)不(bù)能使用HCLK;使用HCLK時(shí)就(jiù)應在(zài)外部截斷時(shí)鍾信号。

降低動态功耗

動态功耗是(shì)在(zài)時(shí)鍾工作且輸入正在(zài)開關時(shí)的(de)功耗。對CMOS電路,動态功耗基本上(shàng)确定了(le/liǎo)總功耗。動态功耗包括幾個(gè)成分,主要(yào / yāo)是(shì)電容負載充電與放電(内部與I/O)以(yǐ)及短路電流。多數動态功率是(shì)内部或外部電容向器件充、放電消耗的(de)。如果器件驅動多個(gè)I/O負載,大(dà)量的(de)動态電流構成總功耗的(de)主要(yào / yāo)部分。

對設計中給定的(de)驅動器,動态功耗由下式計算

p=CL×V 2 DD×f

式中,CL是(shì)電容負載,VDD是(shì)電源電壓,f則是(shì)開關頻率。總功耗是(shì)每個(gè)驅動器功耗之(zhī)總和(hé / huò)。

由于(yú)VDD是(shì)固定的(de),降低内部功耗就(jiù)要(yào / yāo)降低平均邏輯開關頻率,減少每個(gè)時(shí)鍾沿處的(de)邏輯開關總數、減少連線網絡,特别是(shì)高頻信号連線網絡中的(de)電容值。對低功率設計,需要(yào / yāo)從系統至工藝的(de)每個(gè)設計級别中采取相應預防措施,級别越高,效果越好。